#### DOI: 10.15276/aait.01.2021.8 UDC 004. 621.396

#### RESEARCH OF DIGITAL QUBITES FOR HETEROGENEOUS DIGITAL QUANTUM COPROCESSORS

#### Valeriy S. Hlukhov

ORCID: http://orcid.org/0000-0002-0542-7447; valeriygl@ukr.net Lviv Polytechnic National University, 12, Bandera Str. Lviv, Ukraine

#### ABSTRACT

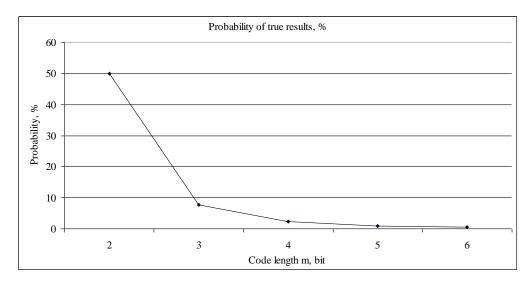

Recently, interest is growing towards real quantum computers, which are analog and probabilistic devices by nature. The interest is also growing to their digital version, both software and hardware. One approach to the construction of real quantum computers is to use quantum chips. The hardware implementation of digital quantum computers involves the use of field programmable gate arrays. A digital quantum coprocessor has already been created which has over a thousand digital qubits and can perform such complex algorithms as a quantum Fourier transformation. The created and working digital quantum coprocessor can already be used to work out various quantum algorithms, algorithms for the interaction of a classic computer and its quantum coprocessor, as well as for research various options for building digital qubits. The purpose of this work is to study the effect of the accuracy of the presentation of the state of digital qubit on the probability of obtaining the correct results of the digital quantum coprocessor. For the study, a heterogeneous digital quantum coprocessor with thirty two digital qubits is selected, which will perform the Fourier quantum transformation. The article describes the basics of building digital quantum coprocessors. Schemes that illustrate the interaction of a classic computer and a quantum coprocessor, the architecture of the coprocessor and the possible structures of its digital qubits are given. Two variants of the coprocessor, homogeneous one with one pseudo-random codes generator and one comparator, and heterogeneous one, with a generator and a comparator in each digital quantum cell, from which digital qubits consist, are shown. Two options for comparators are also shown - with a direct functional converter and with reverse one. In this work, the influence of the length of the qubit state codes of heterogeneous digital quantum coprocessors on the probability of the correct results formation is investigated. It was shown that the probability of obtaining the correct results at the output of the digital heterogeneous coprocessor is sharply (up to fifty percent) improved with a decrease of the qubit state code length, that is, with a decrease in the coprocessor hardware cost. With a length of a code equal to two bits, the quality of the operation of the heterogeneous coprocessor becomes commensurate with the quality of the homogeneous one. The need for additional research in this direction, including with homogeneous coprocessors, is shown.

Keywords: Quantum coprocessor; homogeneous coprocessor; heterogeneous coprocessor; digital qubit; quantum transformation

For citation: Hlukhov V. S. Research of Digital Qubites for Heterogeneous Digital Quantum Coprocessors. Applied Aspects of Information Technology. 2021; Vol.4 No.1. 91–99. DOI: 10.15276/aait.01.2021.8

#### INTRODUCTION. FORMULATION OF THE PROBLEM

Recently, interest is growing towards real quantum computers, which are analog devices by nature. The interest is also growing to their digital version, both software [1] and hardware. One approach to the construction of real quantum computers is to use quantum chips. The hardware implementation of digital quantum computers involves the use of field programmable gate arrays (FPGA).

Digital quantum computers have already passed a long development path – ranging from the development and study of the behavior of their main elements (digital qubits) and ending with the development and study of infrastructure, which allows them to be effectively used.

Quantum computers are designed to perform quantum algorithms.

Quantum algorithms are a mixture of classical logic and quantum routines which can be executed on the quantum chip. According to [2] a quantum computer consists of both a classical and quantum computing part. In [2] heterogeneous quantum computer architecture was presented.

In this work, it is proposed to execute quantum routines in quantum computer not on the quantum chip but on the chip of a digital field programmable gate array, on a FPGA. This paper presents the architecture of such FPGA – architecture of digital quantum coprocessor.

In [3] heterogeneous and homogeneous digital quantum coprocessors are considered. It is important to note that a heterogeneous quantum computer and proposed heterogeneous quantum coprocessor are completely different concepts.

Von Neumann architecture had for a long time a single processor. Then homogeneous multi-core processor dominated the processor development. In

<sup>©</sup> Hlukhov V. S. 2021

This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/4.0/deed.uk)

the era of microprocessors, the understanding came that heterogeneity is the best way forward to improve the compute power. System architecture with heterogeneous accelerators includes the main CPU and heterogeneous coprocessors such as floating point math coprocessors, graphics and neural accelerators, FPGAs. In [2] and [4] heterogeneous quantum computer which consists of a main CPU and a quantum accelerator has been proposed. In this paper heterogeneous quantum computer which consists of a main CPU and a FPGA-based quantum accelerator (coprocessor) has been proposed. And these FPGA-based digital quantum coprocessors can have a homogenous or heterogeneous structure and can be used at the lowest level of full-stack quantum accelerators along with quantum chips and quantum simulators [4].

A quantum computer contains N qubits and a digital quantum coprocessor contains N digital qubits. In both cases as a result of any calculations they can produce any of  $2^{N}$  results. But the same calculations can lead to different results. And every i-th result will be produced with probability  $p_i$ .

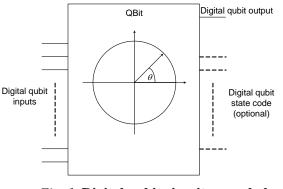

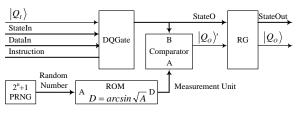

A qubit can be thought of as a device that has a group of inputs for data and instructions that control its behavior. Unlike a real qubit, a digital qubit can have an additional group of outputs. The exact qubit state code is generated on this group of outputs. An important element of the digital qubit is a pseudo random number generator (PRNG). Together with the qubit state code, the pseudo-random code is used to generate a probabilistic result at the one-bit output of the qubit (Fig. 1) [5].

The DiVincenzo [6] criteria are conditions necessary for constructing quantum computer. Not a single word about the physical nature of a quantum computer is included in these criteria. Therefore, you can try to create digital quantum computer. It can be created either as a software model or as a hardware device.

The number of qubits required for solving practical problems is now estimated at several thousand [7]. Creating a true quantum computer with so many qubits is a very difficult task, and a digital quantum coprocessor can already be created on one FPGA.

Recently, other developers have also tried to connect digital technologies with true quantum computers:

place true qubits on the crystal and organize interaction between them using digital methods [8];

it uses a custom crystal that can operate at ultralow temperatures (near 4° K);

- carry out optical control of true qubits embedded in the chip [9];

– use a pseudo-random number generator in true quantum computers [10].

A digital quantum coprocessor has already been created which has 1024 digital qubits and can perform such complex algorithms as a quantum Fourier transformation [11]. Such a transformation is part of the Shor's algorithm [12].

The created and working digital quantum coprocessor [13], [3], can already be used to work out various quantum algorithms, algorithms for the interaction of a classic computer and its quantum coprocessor, as well as for research various options for building digital qubits.

The purpose of this work is to study the effect of the accuracy of the presentation of the state of digital qubit on the probability of obtaining the correct results of the digital quantum coprocessor.

For the study, a heterogeneous digital quantum coprocessor with 32 digital qubits is selected, which will perform the Fourier quantum transformation.

#### THEORETICAL FOUNDATIONS OF QUANTUM COMPUTING

At any moment a classic computer can be exactly in one of the states  $|0\rangle$ ,  $|1\rangle$ , ...,  $|N-I\rangle$  and a quantum computer is simultaneously in all these basic states, in a state of quantum superposition, which is described by a wave function. But during the measurement, the quantum state turns into one of the basic states  $|i\rangle$  with a probability  $p_i$ .

Along with measurement, the quantum superposition can be changed under external influence.

The quantum state is described by a wave function

$$\left|\psi\right\rangle = \sum_{j=0}^{N-l} \lambda_{i} \left|j\right\rangle, p_{j} = \lambda_{j}^{2},$$

$$P = \sum_{j=0}^{N-l} \lambda_{i}^{2} = I \ [14].$$

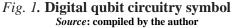

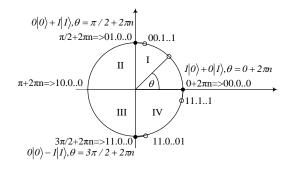

ISSN 2617-4316 (Print) ISSN 2663-7723 (Online) In the simplest case of a single qubit (*Fig. 2*), its wave function change is illustrated by the movement of a single vector [14] either in the Bloch sphere (for complex amplitudes of wave function, [15], [16]) or in a circle (for real amplitudes, [5], [11], [17]). In unit circle for one qubit  $p_0 = \cos^2 \theta$  and  $p_1 = \sin^2 \theta$  respectively.

#### Fig. 2. A Bloch sphere (left) and a unit circle (right) Source: compiled by the author

A true quantum computer is an analog device and it has no memory. It has only gates. Therefore, there are no quantum programs. In the drawing of a true analog quantum computer, a sequence of quantum gates shows only the time sequence of qubit state changes. Software tool [1] allows creating circuits from quantum gates, simulating their work and managing it with C-like language instructions. This is very similar to the FPGA design.

In the schema of a digital quantum computer, a sequence of digital quantum gates shows both the time sequence of qubit state changes and the relative physical position of the

can be an electron spin. An electron can change its spin in time from 1 to 20 nanoseconds [18]. This time can gates themselves in the FPGA.

A good illustration of a qubit serve as a base operation time for compare the performance of true and digital quantum coprocessors.

To compare the capabilities of true and digital quantum computers, one can calculate the quantum volume as a metric that measures the performance of a quantum computer's capabilities and probability that the qubit will work for some time t without failure. Quantum volume QV is a metric that measures the performance of a quantum computer's capabilities and error rates [14]. In the simplest case, the quantum volume is  $QV=p(t)\cdot N$ , where p(t) is probability that qubit will work in time t

$p(t) = e^{-\lambda t} = e^{-t/T}$ ,  $\lambda$  is failure in time (FIT), T is mean time between failures (MTBF), N is qubits number. Now the quantum volume of a real quantum computers is very small (at the level of milliseconds), but for digital quantum coprocessors it is practically unlimited.

For true qubits MTBF is microseconds and millisecond and p(t) run to 0 when t > 1 ms,  $QV \ll N$ .

For digital qubits MTBF is practically unlimited (MTBF of modern FPGA is at level 50 years) and p(t) run to 1. So for digital quantum coprocessor QV = N.

All this speaks about the prospects of creating hardware digital quantum computers.

## THE STRUCTURE OF THE STUDIED DIGITAL QUANTUM COPROCESSOR

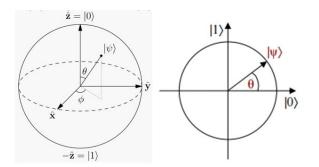

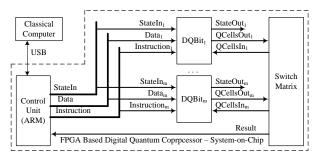

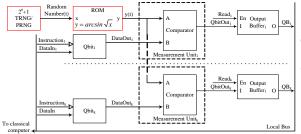

A classical computer controls the operation of a quantum coprocessor (Fig. 3) provides it with an input data, instructions and checks the result of its work [5]. This interaction is well described as a full-stack of the layers of an accelerator at [4].

#### Fig. 3. A classical computer with quantum coprocessor Source: compiled by the author

A generalized functional diagram of full-stack hardware resources of quantum computer with realized in FPGA quantum coprocessor is given in Fig. 4 [5].

The top-level functionality of this stack is provided by the classic host computer. Functioning at the microarchitecture level is provided by embedded in FPGA microprocessor (ARM, control unit).

And directly quantum computing is provided by a set of digital qubits and a switch matrix which connects the qubits to each other and transmits the final state code of all of them or only those required at the moment to the control unit.

#### Fig. 4. A digital quantum coprocessor for classical computer Source: compiled by the author

The connections between qubits can be static or dynamic. In this work static connections have been used. They do not change while the computer is running.

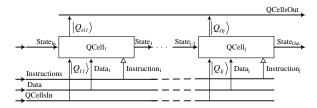

A digital qubit consists of j series-connected digital quantum cells (Fig. 5).

### Fig. 5. RISC processor-like structure of a digital qubit DQBit Source: compiled by the author

Such a connection is similar to the connection of stages in a RISC processor. Every digital quantum cell performs a single operation that changes the state code of a qubit and its measured state  $|Q_{oj}\rangle$ . The state code State<sub>j</sub> changed in one quantum cell is transmitted to the input of the next cell. The first cell in the chain receives an initial state code from a control unit. The state code of the last cell is the

instructions and data from the coprocessor control unit. It also receives the measured states  $\left| Q_{lj}

ight

angle$  of

resulting qubit state code. Each cell receives

another qubits from the coprocessor switch matrix.

Each digital quantum cell includes a digital quantum gate; a state measurement unit (comparator), a pipeline registers RG and functional transformer and PRNG. PRNG provides the formation of probabilistic results of the qubit operations.

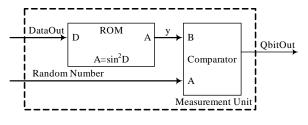

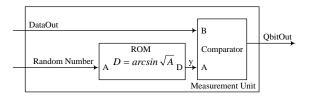

Two types of comparison units are possible:

- with a functional converter  $A = sin^2 D$  at the output of the quantum gate (with direct transformation, Fig. 6);

- with a functional converter  $D = \arcsin \sqrt{A}$  at the PRNG output (with reverse transformation, Fig. 7).

# Fig. 7. A measurement unit with reverse transformer Source: compiled by the author

In this work each digital quantum cell includes a digital quantum gate, a measurement unit, a pipeline register (RG, Fig. 8) and reverse functional transformer  $D = \arcsin \sqrt{A}$  in the output of PRNG. PRNG provides the formation of probabilistic results of the qubit operations.

#### Fig. 8. A digital quantum cell QCell Source: compiled by the author

A digital quantum gate transforms the input qubit state code into the output code under the influence of the instructions and their data, as well as under the influence of measured states of another qubits.

Reverse functional transformation allows the creation and research of two types of digital quantum coprocessors:

each quantum cell of the heterogeneous coprocessor has its own pseudo-random number generator and its own functional transformer;

– a homogeneous coprocessor contains only one pseudo-random number generator and only one functional transformer for all quantum cells, for all quantum qubits (Fig. 9).

Comparison of homogeneous and hetero-geneous digital quantum coprocessors that had up to 1024 qubits was performed in [13], [3]. It was shown that the frequency of the formation of the true results when performing a Fourier quantum transformation in homogeneous coprocessors is higher than that of heterogeneous more than 7 times.

Fig. 9. Homogenous quantum coprocessor Source: compiled by the author

In this study digital quantum coprocessors were implemented for the case of wave function real amplitudes (Fig. 2) and for polar coordinate system to represent the movement of the vector (Fig. 10) [11].

As can be seen from Fig. 10 the state of the digital qubit is determined by the angle  $\theta$ , which in the quadrant I take values from 0 to  $\pi/2$  radians. For encoding these values, binary codes from 00... 0 to 10 ... 0 are selected. The length of these codes is L = m+1.

#### Fig. 10. A polar coordinate system (angle θ codes) Source: compiled by the author

In this paper, the effect of the length L of the state codes of heterogeneous digital quantum coprocessors on the frequency of the formation of the correct results is investigated. In these studies, the variable value was m.

Study design steps are standard for FPGA design:

to create or to find an algorithm for solving the problem;

to find or to create a mathematical description of the solution to the problem;

for FPGA-based circuits to create graphic symbols of library elements and their descriptions in hardware description language;

to create a schema from library elements;

- to simulate the created schema;

- to implement the project;

- to verify the project;

to make a prototype project.

To make all these actions, an IP Core generator (a generator of VHDL-descriptions) of the elements of the digital quantum coprocessor was developed.

The IP Core generator was developed to create VHDL descriptions of digital quantum elements and schema of digital quantum coprocessors in general.

# THE DIAGRAM OF A DIGITAL QUANTUM COPROCESSOR SELECTED FOR STUDIES

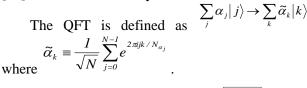

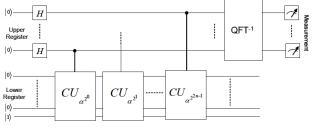

The quantum Fourier transform (QFT) as a part of Shor's algorithm [12] (Fig. 11) for factorization [19] was chosen for study.

## Fig. 11. Quantum factorization by Shor's algorithm Source: compiled by the author

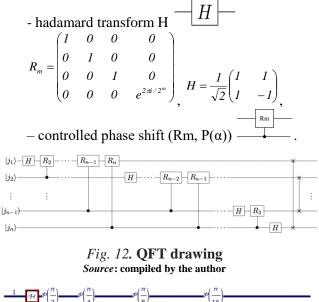

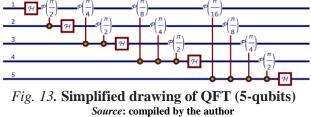

Only 2 types of digital quantum gates are required during QFT (Fig. 12; Fig. 13):

| From/to<br>Classical<br>Computer | Control<br>FSM | $\downarrow$ $\downarrow$ $QI_0$ | Qgate <sub>0_0</sub><br>Load | $\begin{array}{c} \mathbf{q}_{0_{-0}} \\ \hline \mathbf{Q}_{0_{-0}} \\ \hline \end{array}$                | Qgate <sub>0_1</sub><br>Had | $\begin{array}{c} \mathbf{q}_{0\_1} & \mathbf{q}_{1\_0} \\ \hline \mathbf{Q}_{0\_1} & \hline \mathbf{Q}_{0\_1} \end{array}$ | Qgate <sub>0_2</sub><br>Add<br>Pi/2                                            | $\begin{array}{c} \mathbf{q}_{0_2} & \mathbf{q}_{2_0} \\ \mathbf{Q}_{0_2} & \mathbf{q}_{2_0} \\ \mathbf{Q}_{0_2} & \mathbf{q}_{0_2} \end{array}$ | Qgate <sub>0_3</sub><br>Add<br>Pi/4 | $\xrightarrow{\mathbf{q}_{0_3}} \mathbf{q}_{3_0}$                                                | Qgate <sub>0_4</sub><br>Add<br>Pi/8 | $\xrightarrow{\mathbf{q}_{0_4}=\mathbf{q}\mathbf{o}_3}_{\mathbf{Q}_{0_4}}$   |

|----------------------------------|----------------|----------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------|

|                                  |                | $\xrightarrow{1}{QI_1}$          | Qgate <sub>1_0</sub><br>Load | $\xrightarrow{q_{1_0}} \xrightarrow{1}$                                                                   | Qgate <sub>1_1</sub><br>Had | $\xrightarrow{\mathbf{q}_{1\_1}}_{\mathbf{Q}_{1\_1}} \xrightarrow{\mathbf{q}_{2\_0}}$                                       | $\begin{array}{c} \text{Qgate}_{1_2} \\ \text{Add} \\ \text{Pi/2} \end{array}$ | $\xrightarrow{\mathbf{q}_{1_2}}_{\mathbf{Q}_{1_2}} \xrightarrow{\mathbf{q}_{3_0}}$                                                               | Qgate <sub>1_3</sub><br>Add<br>Pi/4 | $q_{1_3}$ $1$ $Q_{1_3}$ $\rightarrow$                                                            | Qgate <sub>1_4</sub><br>Load        | $\xrightarrow{\mathbf{q}_{1\_4}=\mathbf{q}\mathbf{o}_2}_{\mathbf{Q}_{1\_4}}$ |

|                                  |                | $\downarrow 1$<br>$QI_2$         | Qgate <sub>2_0</sub><br>Load | $\xrightarrow{q_{2},0} \xrightarrow{1}$                                                                   | Qgate <sub>2_1</sub><br>Had | $\xrightarrow{\mathbf{q}_{2_1}} \underbrace{\mathbf{q}_{3_0}}_{\mathbf{Q}_{2_1}}$                                           | $\begin{array}{c} Qgate_{2_2} \\ Add \\ Pi/2 \end{array}$                      | $\xrightarrow{\mathbf{q}_{2,2}} \underbrace{\mathbf{q}_{2,2}}_{\mathbf{Q}_{2,2}} \xrightarrow{1}$                                                | Qgate <sub>2_3</sub> ·<br>Load      | $\xrightarrow{q_{2_3}} \xrightarrow{1}$                                                          | Qgate <sub>2_4</sub><br>Load        | $\xrightarrow{\mathbf{q}_{2_4}=\mathbf{qo}_1}_{\mathbf{Q}_{2_4}}$            |

|                                  |                | $\downarrow$ $QI_3$              | Qgate <sub>3_0</sub><br>Load | $\begin{array}{c} \mathbf{q}_{3,0} & 1 \\ \mathbf{Q}_{3_{-}0} & 1 \\ \mathbf{Q}_{3_{-}0} & 1 \end{array}$ | Qgate <sub>3_1</sub><br>Had | $\begin{array}{c} \mathbf{q}_{3\_1} & 1 \\ \mathbf{Q}_{3\_1} & 0 \\ \mathbf{Q}_{3\_1} & 0 \end{array}$                      | Qgate <sub>3_2</sub><br>Load                                                   | $\begin{array}{c} \mathbf{q}_{3,2} \\ \hline \mathbf{Q}_{3,2} \\ \hline \end{array}$                                                             | Qgate <sub>3_3</sub> ·<br>Load ·    | $\xrightarrow{\mathbf{q}_{3\_3}} \underbrace{\overset{1}{}}_{\mathbf{Q}_{3\_3}} \xrightarrow{1}$ | Qgate <sub>3_4</sub><br>Load        | $\xrightarrow{\mathbf{q}_{3_4}=\mathbf{q}\mathbf{o}_0}_{\mathbf{Q}_{3_4}}$   |

Fig. 14. FPGA schema of QFT (4-qubit) Source: compiled by the author

When implementing a digital qubit in the form a chain of digital quantum gates and of implementing only a QFT circuit on FPGA, there is no need to change the functions of the quantum gates. Therefore, the functions of each gate are determined only by their circuit. And there is no need for instructions that change the function of the gates. Therefore, they are not shown in the Fig. 14, but are shown in the general diagram Fig. 4. And the data path in the Fig. 14 is a chain of links named Q\*, along which the changing qubit state code goes from one gate to another. The measured states of a qubit, which are called q\*, are transferred from one gate to another as required by the algorithm for solving the problem.

QFT determines spectrum of qubits states.

The work studied the performance of QFT with the use of 32 qubits.

#### THE DIGITAL QUANTUM COPROCESSOR SELECTED FOR STUDIES

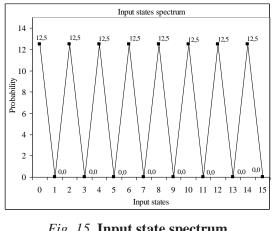

For analysis the input state of qubits, which can conditionally be described as  $|XXX..X0\rangle$ , where X corresponds to the neutral position of the vector in the unit circle – at angle of  $\pi/4$ , was selected. The probability of measuring the input state with odd code is p<sub>odd</sub>=0, and with even codes is p<sub>even</sub> =  $100/2^{n-1}$ %, where n is qubits quantity and the spectrum of qubit states at the QFT input will look like in Fig. 15 (for 4 qubits).

QFT must determine the frequency (number of periods) of such a graph. The correct result is 8. 32 qubits were used in the work. Their state  $|xxx...x0\rangle$  forms a graph with the number of periods equal to  $2^{32-1}$ . The probability of the appearance of the true results at the output of the digital quantum coprocessor, which performs QFT, depending on the length of the codes of its qubits is shown on Fig. 16.

In [13], the quality of the operation of homogeneous and heterogeneous coprocessors, in which the length of the qubits state code was equal to 3, was tested. Homogeneous coprocessors have shown 7 times better quality of work (the probability of obtaining the true results).

$$(\theta_3 = \theta_2 = \theta_1 = 45^\circ, \theta_0 = 0^\circ)$$

Source: compiled by the author

As can be seen from Fig. 16, the quality of the operation of a digital heterogeneous coprocessor is dramatically improved with a decrease in the length of the qubit state code, that is, with a decrease in the hardware costs to build a coprocessor. With a length of 2 bits, the quality of the operation of the heterogeneous coprocessor becomes commensurate with the quality of the operation of a homogeneous one. This sharply contrasts with the results of work [13].

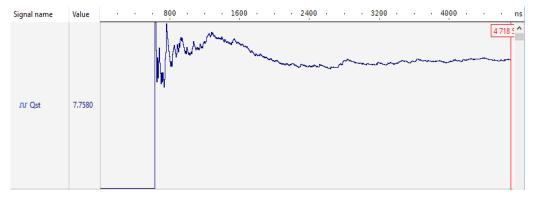

To determine the probability of the appearance of the correct results at the output of the digital quantum coprocessor in each experiment, 4096 the same measurements were carried out. The graph of changing the probability during one of the experiments (with the length of the qubit state code of 3 bits) is shown in the Fig. 17.

*Fig. 16.* The probability of the correct results, depending on the length of the qubit state code *Source:* compiled by the author

Fig. 17. The probability of the correct results, depending on the duration of the study (on the number of experiments) Source: compiled by the author

On the graph, the frequency of the appearance of the correct results begins to be displayed after the 10th measurement (left vertical line) and ends after the 4096th measurement (right vertical line). The final probability values are marked on Fig. 16.

As can be seen, as a result of this study, unexpected results were obtained, which logically brings to the need for additional research. Studies similar to those described in this paper must be carried out with homogeneous coprocessors. Additionally, it is necessary to check the detected dependencies for other combinations of states at the input of the quantum Fourier transform unit, for coprocessors with another qubit numbers, evaluate changes in the hardware costs to implement each digital quantum coprocessor.

#### CONCLUSIONS

1. The paper presents the schemes of homogeneous and heterogeneous quantum coprocessors.

2. The study of the probability of obtaining the true results by a heterogeneous quantum coprocessor was carried out depending on the state code length of its digital qubits.

3. It is shown that the specified probability increases sharply (up to 50 %) with a decrease of the state code length, that is, with a decrease in the hardware cost of coprocessor.

4. The need for additional studies in this direction, including with homogeneous coprocessors, is shown.

#### REFERENCES

1. "Microsoft Quantum Documentation". 2020. – Available from: https://docs.microsoft.com. – [Accessed: May, 2020].

2. Fu, X., Riesebos, L., Lao, L. et al. "A heterogeneous quantum computer architecture". In 2016 ACM

International Conference on Computing Frontiers (CF'16). 2016. p. 323–330. DOI: 10.1145/2903150.2906827.

3. Hlukhov, V. "FPGA Based Digital Quantum Computer Verification". In 2020 IEEE 11th International Conference on Dependable Systems, Services and Technologies (DeSSerT). 2020. p. 178–182. DOI: 10.1109/DESSERT50317.2020.9125077.

4. Bertels, K., Sarkar, A., Hubregtsen, T., Serrao, M., Mouedenne, A., Yadav, A., Krol, A. & Ashraf, I. "Quantum Computer Architecture: Towards Full-Stack Quantum Accelerators". In 2020 EDAA Design, Automation & Test in Europe Conference & Exhibition (DATE). 2020. p. 1–6. DOI: 10.23919/DATE48585.2020.9116502.

5. Hlukhov, V. & Havano, B. "FPGA-based Digital Quantum Coprocessor". *Advances in Cyber-Physical Systems*. 2018; 3(2): 12–31. DOI: 10.23939/acps2018.02.067.

6. DiVincenzo, D. "The physical implementation of quantum computation". *Fortschritte der Physik: Progress of Physics*. 2000; 48 (9–11): 771–783.

7. "Applying Moore's Law to Quantum Qubits". *Quantum Computing Report.* – Available from: https://quantumcomputingreport.com/our-take/applying-moores-law-to-quantum-qubits. 2019. – [Accessed: Nov, 2020].

8. Moore, S. "What Intel Is Planning for The Future of Quantum Computing: Hot Qubits, Cold Control Chips, and Rapid Testing". *IEEE Spectrum*, 2020. – Available from: https://spectrum.ieee.org/tech-talk/computing/hardware/intels-quantum-computing-plans-hot-qubits-cold-control-chips-and-rapid-testing. – [Accessed: Aug, 2020].

9. Anderson, Ch.P., Bourassa, A., Miao, K.C., Wolfowicz, G., Mintun, P.J., Crook, A.L., Abe, H., Hassan, J.U., Son, N.T., Ohshima, T. & Awschalom, D. D. "Electrical and optical control of single spins integrated in scalable semiconductor devices". *Science*. 2019; 366(6470): 1225–1230. DOI: 10.1126/science.aax9406.

10. Miyamoto, K. & Shiohara, K. "Reduction of Qubits in Quantum Algorithm for Monte Carlo Simulation by Pseudo-random Number Generator". *Physical Review A*. 2020. 022424. DOI: 10.1103/physreva.102.022424.

11. Hlukhov, V. "Implementing quantum Fourier transform in a digital quantum coprocessor". *Advances in Cyber-Physical Systems*. 2019; 4(1): 6–13. DOI: 10.23939/acps2019.01.006.

12. Shor, P. "Polynomial-Time Algorithms for Prime Factorization and Discrete Logarithms on a Quantum Computer". In *35th Annual Symposium on Foundations of Computer Science*. 1994; p. 124–134. – Available at: https://www.jstor.org/stable/2653075?seq=1. – Accessed 25 Nov. 2020.

13. Hlukhov, V. "FPGA-Based Homogeneous and Heterogeneous Digital Quantum Coprocessors". Advances in Science, Technology and Engineering Systems Journal (ASTESJ). 2020; 5(6): 1643–1650. DOI: 10.25046/aj0506195.

14. Grumbling, E., Horowitz, M. (eds.). "Quantum computing: progress and prospects". *The National Academies of Sciences, Engineering, and Medicine*. Washington: DC: *National Academies Press*. 2019.

15. Khalil-Hani, M., Lee, Y. & Marsono, M. "An accurate FPGA-based hardware emulation on quantum Fourier transform". In *13th Australasian Symposium on Parallel and Distributed Computing (AusPDC 2015)*. 2015. p. 23–30.

16. Gushanskiy, S. & Pereverzev, V. "Simulation of quantum computing using hardware cores" (in Russian). *Scientific Journal of KubSAU*, 2016; 123(09): 545–557. – Available from: http://ej.kubagro.ru/2016/09/pdf/37.pdf. – [Accessed: Dtc, 2020].

17. Hlukhov, V. "FPGA-based K-qubit digital quantum coprocessor". *Electrotechnic and Computer Systems*. 2019; 31(107): 104–117. DOI: 10.15276/eltecs.31.107.2019.10.

18. Smith, J., Dalgarno, P., Warburton, R., Govorov, A., Karrai, K., Gerardot, B. & Petroff, P. "Voltage control of the spin dynamics of an exciton in a semiconductor quantum dot". *Phys. Rev. Lett.* 2005; 94 197402.

19. Hlukhov, V. "Comparison of Homogeneous and Heterogeneous Digital Quantum Coprocessors". In *International Workshop on Computational Methods and Information Transformation Systems, a satellite of IEEE 2020 XV International Scientific and Technical Conference on Computer Science and Information Technologies.* 2020. p. 70–73.

Conflicts of Interest: The authors declare no conflict of interest

Received03.02.2021Received after revision12.03.2021Accepted15.03.2021

DOI: 10.15276/aait.01.2021.8 УДК 004. 621.396

#### ДОСЛІДЖЕННЯ ЦИФРОВИХ КУБІТ ДЛЯ НЕОДНОРІДНИХ ЦИФРОВИХ КВАНТОВИХ КОПРОЦЕСОРІВ

#### Валерій Сергійович Глухов

ORCID: http://orcid.org/0000-0002-0542-7447; valeriygl@ukr.net Національний університет «Львівська політехніка», вул. С. Бандери, 12, Львів, Україна

#### АНОТАЦІЯ

Останнім часом разом із зростанням інтересу до квантових комп'ютерів (до реальних квантових комп'ютерів, які за своєю природою є аналогові та ймовірнісні пристрої), зростає інтерес і до їх цифрових версій, як програмних, так і апаратних. Апаратна реалізація цифрових квантових комп'ютерів передбачає використання програмованих логічних інтегральних мікросхем. Уже створено цифровий квантовий копроцесор, який має в своєму складі понад тисячу цифрових кубіт і може виконувати такі складні алгоритми як квантове перетворення Фур'є. Створений і працездатний цифровий квантовий копроцесор вже зараз можна використовувати для відпрацювання різних квантових алгоритмів, алгоритмів взаємодії класичного комп'ютера і його квантового копроцесора, а також для дослідження різних варіантів побудови цифрових кубіт. Метою даної роботи як раз і є дослідження впливу точності представлення стану цифрового кубіта на ймовірність отримання правильних результатів цифровим квантовим копроцесором. Для дослідження обрано неоднорідний цифровий квантовий копроцесор з тридцятьма двома цифровими кубітами, який виконує квантове перетворення Фур'є. У статті описано основи побудови цифрових квантових копроцесорів. Наведено схеми, які ілюструють взаємодію класичного комп'ютера і квантового копроцесора, архітектуру копроцесора і можливі структури його цифрових кубіт. Показано два варіанти копроцесора – однорідний, з одним генератором псевдовипадкових кодів і одним компаратором, і неоднорідний, з генератором і компаратором в кожній цифровій квантовій комірці, з яких складаються цифрові кубіти. Також показано два варіанти компараторів – з прямим функціональним перетворювачем та із зворотнім. У цій роботі досліджено вплив розрядності кодів стану кубіта в неоднорідних цифрових квантових копроцесорах на ймовірність формування копроцесорами правильних результатів. Було показано, що ймовірність отримання правильних результатів на виході цифрового неоднорідного копроцесора різко поліпшується до п'ятдесяти відсотків із зменшенням розрядності коду стану кубіта, тобто, із зменшенням апаратних витрат на побудову копроцесора. При розрядності, що дорівнює двом бітам, якість роботи неоднорідного копроцесора стає порівняною з якістю роботи однорідного копроцесора. Показано необхідність проведення додаткових досліджень в цьому напрямку, в тому числі, і з однорідними копроцесорами.

**Ключові слова:** квантовий копроцесор; однорідний копроцесор; неоднорідний копроцесор; цифровий кубіт; квантове перетворення; перетворення Фур'є

#### **ABOUT THE AUTHORS**

Valeriy S. Hlukhov – Dr. Sci. (Eng), Prof. Department of Computer Engineering. Lviv Polytechnic National University. 12, Bandera Str. Lviv, Ukraine ORCID: http://orcid.org/0000-0002-0542-7447; valeriygl@ukr.net *Scientific field*: Computer Systems and Components

Валерій Сергійович Глухов – д-р техніч. наук, проф., проф. каф. Електронних обчислювальних машин Національного університету «Львівська політехніка». вул. С. Бандери, 12, Львів, Україна